Low Power IP Key to Capitalizing on Growth Markets

Gen Z, the successor to the millennials born between 1995 and 2010 may, according to economists and sociologists, ultimately may determine who succeeds and who fails in the semiconductor industry. The oldest Gen Zers are about 22-years old, many are members of the soon-to-be graduation Class of 2018 and are just entering the workforce. So, while the media has focused a lot on millennials, it would behove product planners to turn some of the attention to the millennials’ future co-workers.

Key is that Gen Z is going to be far different from their predecessors. According to Advertising Age, Gen Z is the most diverse and multicultural of any generation in the U.S. – 55% are Caucasian, 24% are Hispanic, 14% are African-American and 4% are Asian. More importantly, they are the true digital natives, never having know a world without They don’t know a world without PCs, mobile phones, gaming devices and MP3 players. They live online, sharing details of their lives across dozens of platforms and dictating what they like and dislike with a tweet, post or status.

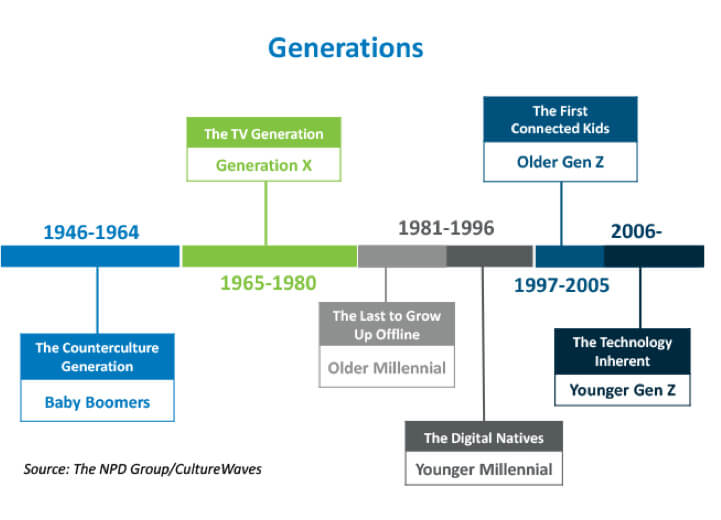

What this should say to the product planners at all points in the semiconductor value chain is that mobility, long batter-life and near-zero power consumption will be key to wooing the next generation of pernickety consumers and that the newly Medical, Wearable and IoT markets will represent the Gen Z sweet spot.

As the diagram below highlights these markets are predicted to grow at over 9% CAGR in the next few years.

However, market success will demand a markedly different design ethos. Performance and bleeding edge advanced process technology will give way to extreme cost sensitive and power consumption. In the case of the IoT market many devices will be “fit and forget” that necessitates extremely low power operation.

Addressing this challenge demands innovation from all eco-system partners but Nowhere is this challenge more pertinent than the creation of low voltage SRAM.

Low Voltage Design Challenges

Whilst the logic may be synthesised to operate at near threshold voltages thereby delivering the requisite power savings the inclusion of SRAM in such circuitry remains a fudge. Underlying this issue is the high-density foundry bit cell. This structure is optimised for packing density and is particularly susceptible to process variation. Statistical considerations mean that a significant minority of a bit cell population (of which there could easily be millions per chip) could be unduly “weak”.

Dual rail SRAM resolves this problem with a correctly powered bit cell array However, the central problem of multiple supply rails and a ring of level shifters to interface to the memory remain. This approach can be made to work, but the impact on physical implementation, verification and timing closure means requires a high degree of manual intervention and its associated challenges.

A Low Voltage Option

sureCore has developed its EverOn™ SRAM specifically for the demanding near threshold environment that has been silicon-proven down to 0.6V across process corners and the full industrial temperature range (-40C to 125C) in a leading 40nm foundry ULP Logic and Embedded Flash process.

EverOn™ is production-ready including an extensive verification environment to demonstrate adequate margins across PVT corners, corner silicon validation and successful completion of life tests. Access to the compiler is via a web-based interface that generates the standard EDA model suite as well as product datasheets.

Near threshold design methodology delivers the dramatic power savings necessary for IoT, Medical and Wearable applications that will be hot on Gen Z’s list of must-have gadgets. With a rich suite of power down modes, EverOn™ delivers improved flexibility, a single supply rail solution and an industry-first capability to track logic operating down to 0.6V.