eFPGAs enable programmability in SoCs for low power products

Montpellier, France, September 6, 2017 — Menta SAS, a leading embedded FPGA (eFPGA) Intellectual Property (IP) provider, and sureCore Ltd., a low-power SRAM IP leader, today opened the doors to creative power-sensitive design in leading-edge applications with the availability of eFPGA IP with embedded sureCore PowerMiser™ low-power SRAM IP. The IP is optimized for the TSMC 28 nanometer process.

Menta’s eFPGAs enable programmability to be embedded into complex SoCs, allowing changes to be made to the RTL at will, post-production, thereby eliminating costly re-spins. This capability is critical to meeting the sometimes conflicting requirements of changing standards, security updates and shrinking time-to-market windows of mobile and consumer products, IoT devices, networking and automotive ICs.

sureCore’s single port synchronous low power PowerMiser IP delivers more than 50% dynamic power savings and up to 38% static power savings compared to today’s commercially available alternatives. PowerMiser is ideal for leading-edge devices demanding long battery life and minimal operating and stand-by power consumption. The macro is process agnostic and silicon proven in both CMOS and FDSOI manufacturing processes.

“Menta is pleased to demonstrate the flexibility of its eFPGA IP by integrating sureCore innovative low-power SRAM,” said Yoan Dupret, Managing Director of Menta. “Adding sureCore SRAM IP within our eFPGA IP and Origami Programmer software only required a couple of weeks thanks to sureCore support and SRAM IP ease of integration.”

“This collaboration represents the first stage in an on-going relationship where sureCore provide custom memory solutions on Menta’s customers’ requests. Our commitment is to help Menta provide forward-looking designs with the lowest power eFPGA,” explained Eric Gunn, sureCore’s Chief Operating Officer.

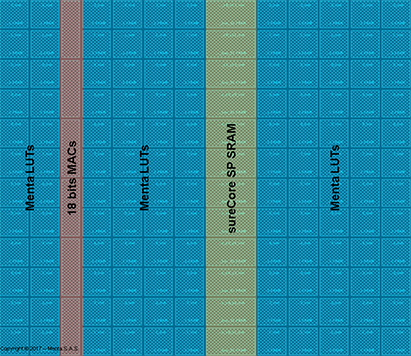

The eFPGA core IP includes 800 LUT6 equivalent, six 18bit MAC and 6Kb of sureCore single port SRAM in the TSMC 28HPC+ technology node running at 0.9V. The new IP targets mobile, base stations and IoT products for applications such as flexible interface bridging, power-up management or sensor hubs. Menta eFPGA IP including sureCore SRAM IP can be customized with various amount of LUTs, DSPs and SRAM based on customer requirements; and in the most widely used 40nm ULP and 28nm LP processes, as well as 28nm FDSOI technology.

Availability

Menta’s eFPGA IP core datasheet and associated software are available now.

For more information, please visit www.menta-efpga.com, or contact their customer support team at info@menta-efpga.com.

Origami Designer, Origami Programmer and eFPGA Core IP are registered trademarks of Menta SAS. All other trademarks and tradenames are the property of their respective holders.